对于基本单元逻辑电路,使用Verilog语言提供的门级元件模型描述电路非常方便。

但随着电路复杂性的增加,使用的逻辑门较多时,使用HDL门级描述的工作效率就很低。

数据流建模能够在较高的抽象级别描述电路的逻辑功能,并且通过逻辑综合软件,能够自动地将数据流描述转换成为门级电路。

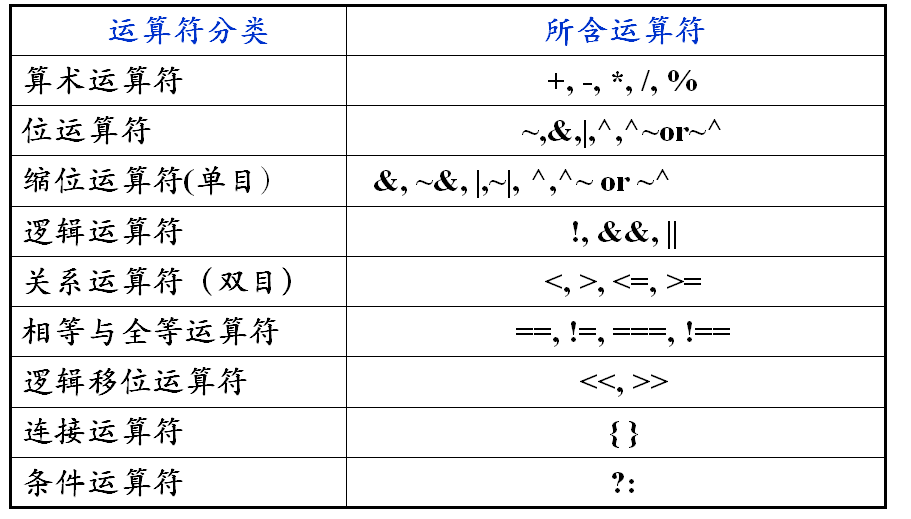

数据流建模主要使用逻辑表达式,所以要了解各种运算符和表达式。

数据流建模使用的连续赋值语句,由关键词assign开始,后面跟着由操作数和运算符等组成的逻辑表达式。

一般用法如下:

wire [位宽说明] 变量名1,变量名2,……,变量名n;

assign 变量名=表达式;

注意,assign 语句只能对wire型变量进行赋值,所以等号左边变量名的数据类型必须是wire型。

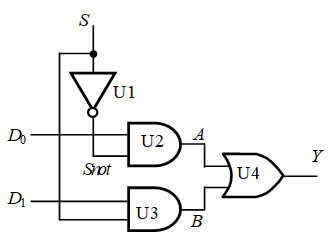

module mux2to1_dataflow(D0, D1, S, Y );

input D0, D1, S;

output Y;

wire Y ;

//下面是逻辑功能描述

assign Y = (~S & D0) | (S & D1); //表达式左边Y必须是wire型

endmodule

module mux2x1_df (D0,D1,S,L);

input D0,D1,S;

output L;

assign L = S ? D1 : D0;

endmodule

条件运算符:如果S=1,则输出L=D1;否则L=D0。

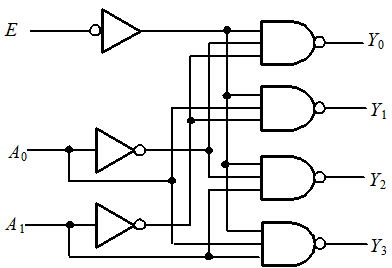

module decoder_df (A1,A0,E,Y);

input A1,A0,E;

output [3:0] Y;

assign Y[0] = ~(~A1 & ~A0 & ~E);

assign Y[1] = ~(~A1 & A0 & ~E);

assign Y[2] = ~( A1 & ~A0 & ~E);

assign Y[3] = ~( A1 & A0 & ~E);

endmodule

作用是将两个或多个信号的某些位拼接起来成为一个新的操作数,进行运算操作。

设A=1’b1,B=2’b10,C=2’b00

则{B,C}=4’b1000

{A,B[1],C[0]}=3’b110

{A,B,C,3’b101}=8’b11000101。

对同一个操作数的重复拼接还可以双重大括号构成的运算符{{}}

例如{4{A}}=4’b1111,{2{A},2{B},C}=8’b11101000。

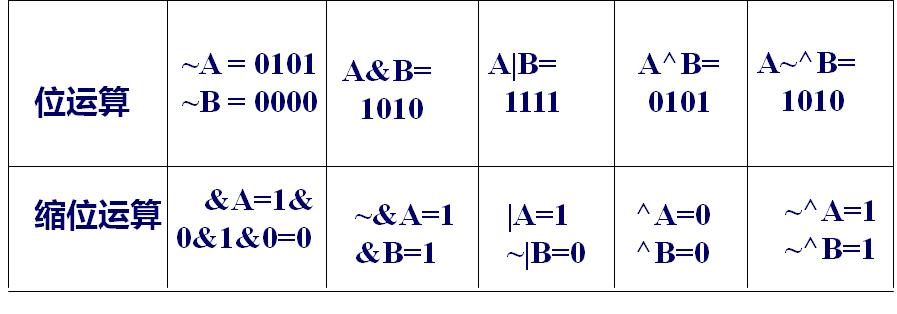

A:4’b1010 、B:4’b1111,

==(逻辑相等), !=(逻辑不等) ===(条件全等),!==(条件不全等)

a、b的初值同为4’b0100,c和d的初值同为4’b10x0

| a= =b | a!=b | a= = =b | a!= =b |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| c= =d | c!=d | c= = =d | c!= =d |

| x | x | 1 | 0 |

是三目运算符,运算时根据条件表达式的值选择表达式。

一般用法:

condition_expr ? expr1 : expr2;

首先计算第一个操作数condition_expr的值,如果结果为逻辑1,则选择第二个操作数expr1的值作为结果返回;如果结果为逻辑0,则选择第三个操作数expr2的值作为结果返回。

优先级的顺序从下向上依次增加。

| 类型 | 符号 | 优先级别 |

|---|---|---|

| 取反 | ! ~ -(求2的补码) | 最高优先级 |

| 算术 | *** /** + - | |

| 移位 | >> << | |

| 关系 | < <= > >= | |

| 等于 | == != | |

| 缩位 | & ~& ^ ^~ | ~| | |

| 逻辑 | && || | |

| 条件 | ?: | 最低优先级 |

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月