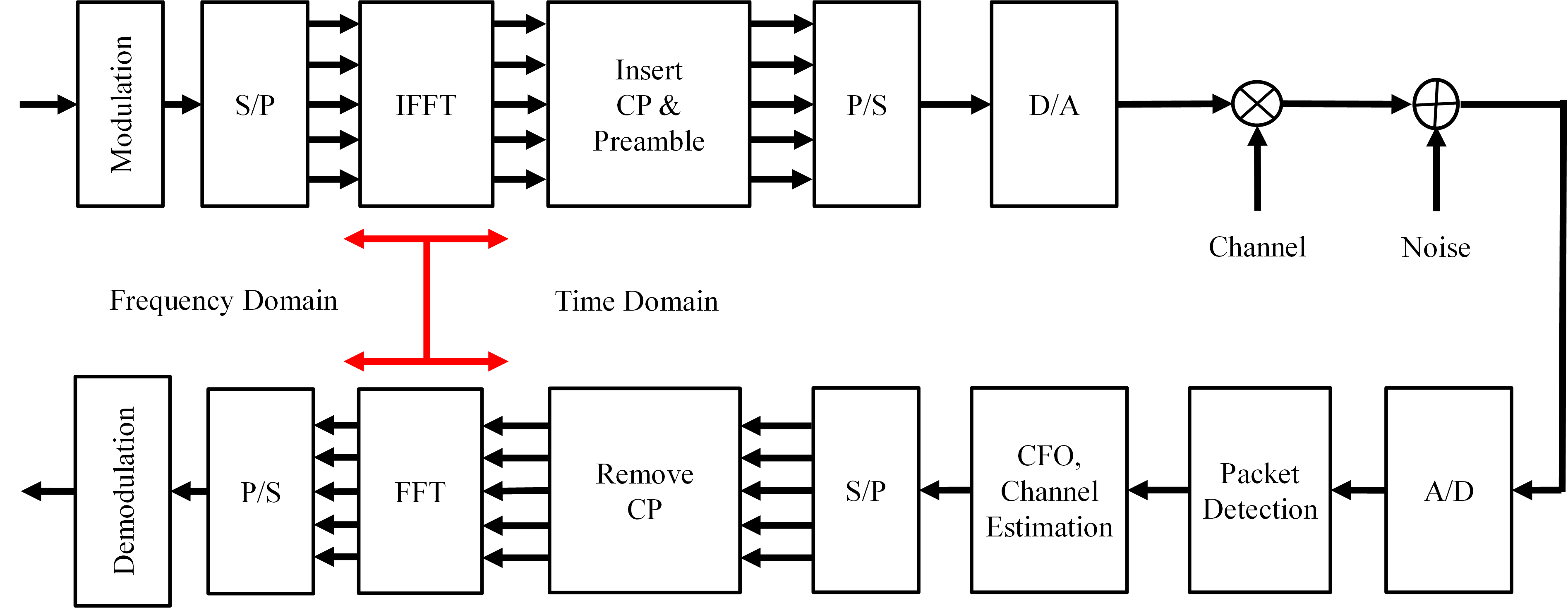

This simple OFDM demo is based on IEEE 802.11a OFDM format for testing SDR hardware.

Using Software Designed Radio (SDR) to transmit OFDM signals at 5 GHz.

Transmitter and Receiver hardware : Zedboard (Xilinx Zynq®-7000) + AD9361 (Analog Device-FMCOMMS3)

- Matlab R2016a

- support package for Xilinx Zynq-Based Radio (R2016a version)

Before executing this code, please follow this tutorial to install support package for Xilinx Zynq-Based Radio in Matlab.

Please open multiple Matlab windows to run Hardware_TX.m and Hardware_RX.m respectively.

TX_signal.mat

OFDM_TX.m

- data_Payload_1.mat

- data_Payload_2.mat

- oversamp.m

OFDM_RX.m

- Long_preamble_slot_Frequency.mat

- setstate0.m

- RX.mat

- RX2.mat

- GUI_TX

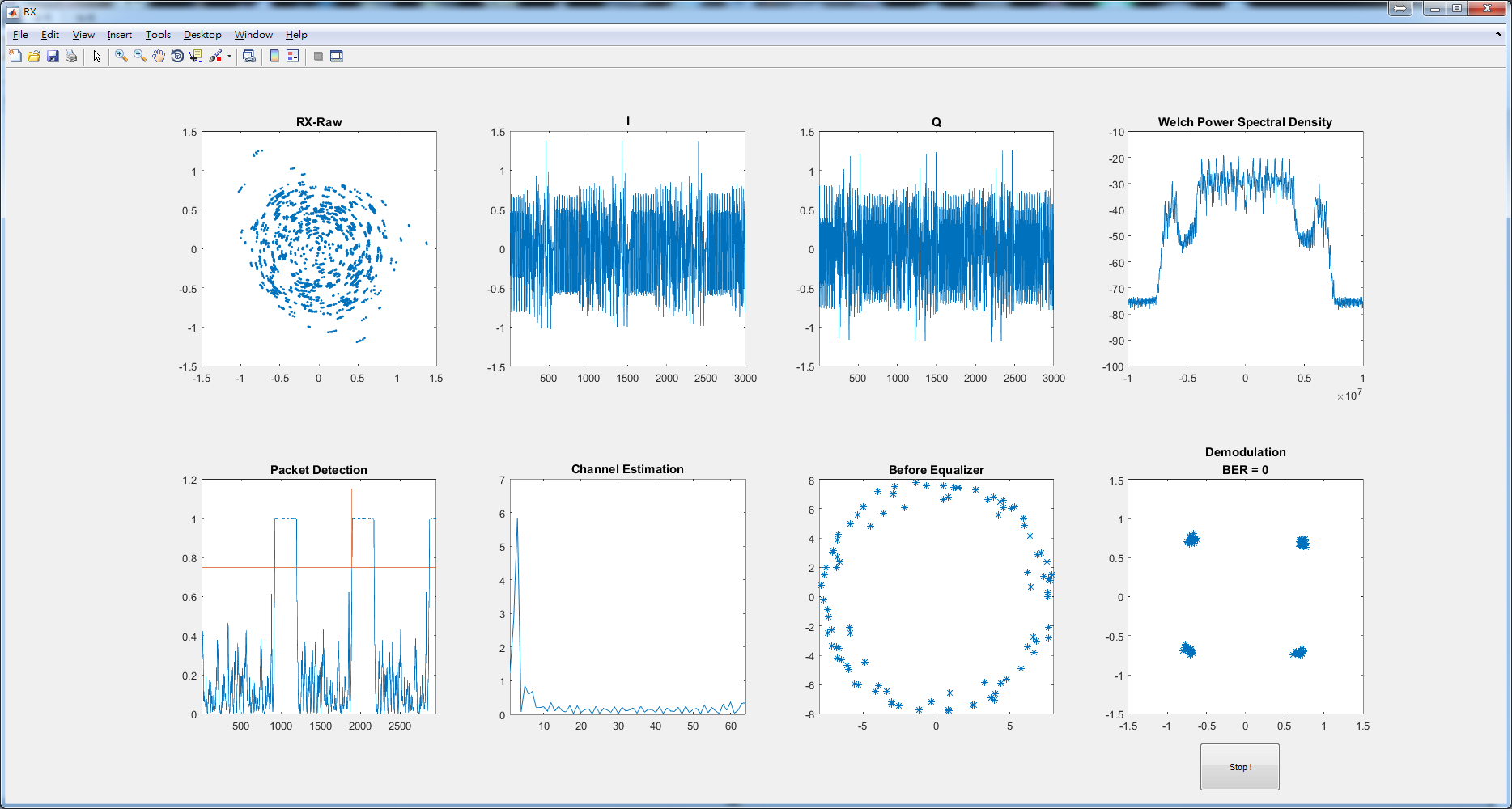

- GUI_RX

Video Demo : https://www.youtube.com/watch?v=gNmMxtsWckw

- Data Signal Mapping

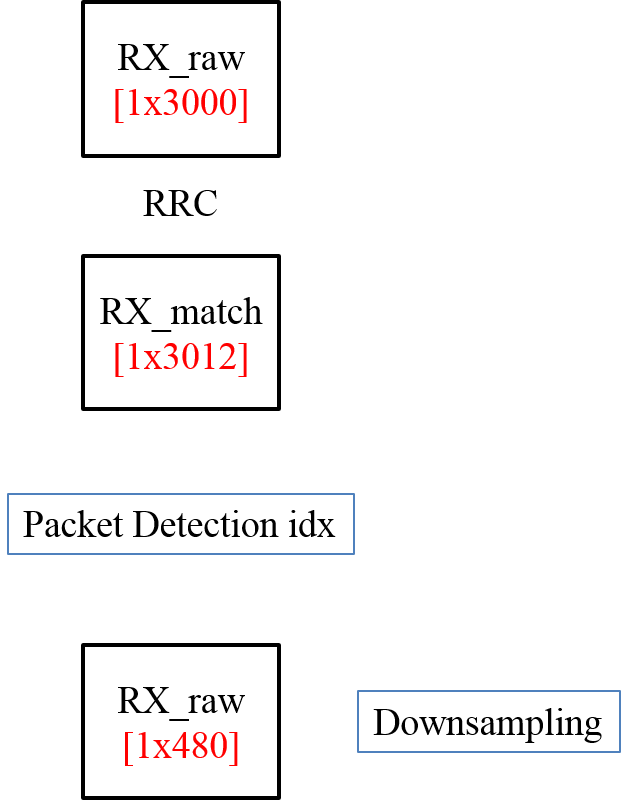

- Packet Detection

- Coarse/Fine Frequency Offset Estimation & Compensation

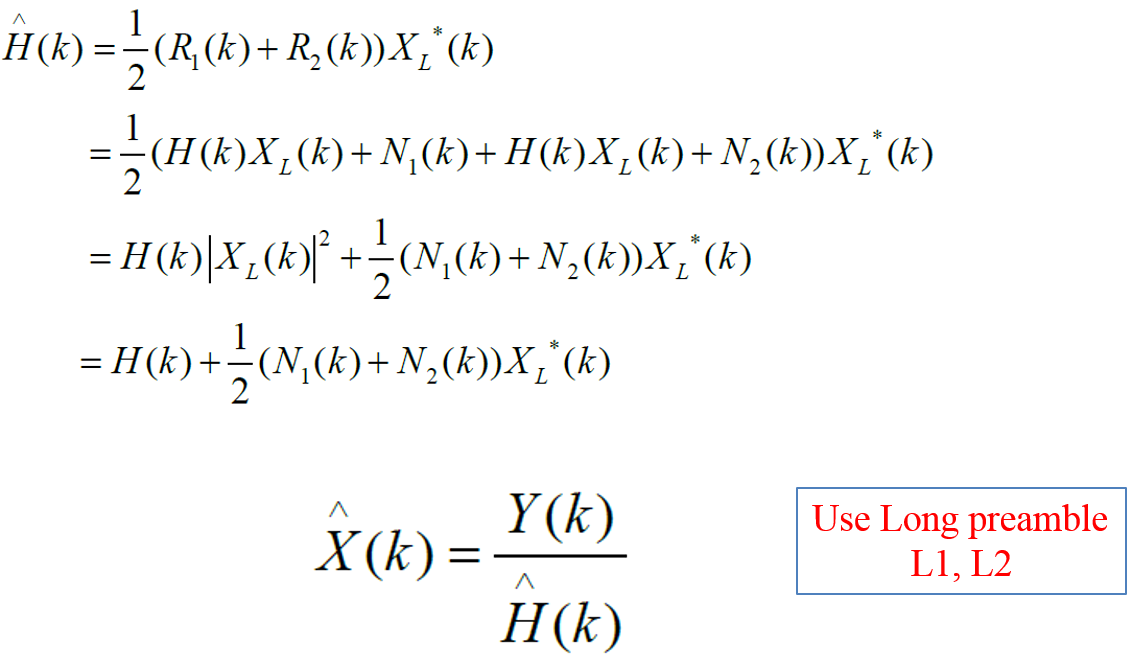

- Channel Estimation & One-Tap Equalizer

- Data De-Mapping

- AGC (Auto Gain Control)

- Fine Symbol Timing Estimation

- Convolutional Decoding

- De-Interleaving

- Frame check calculation (It assumes every packet is the same length)

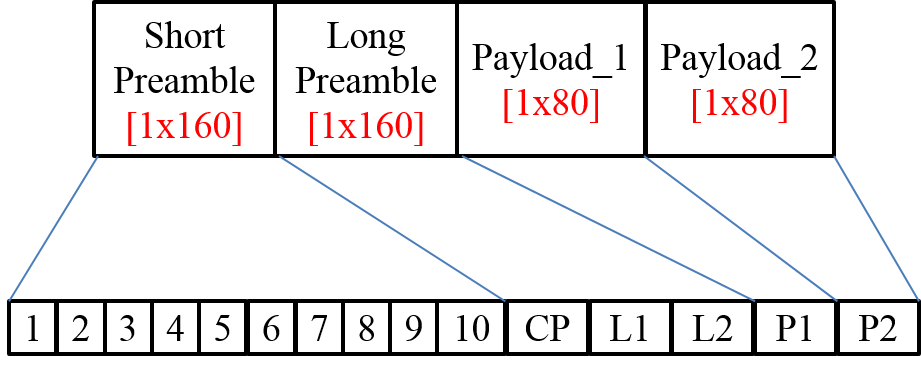

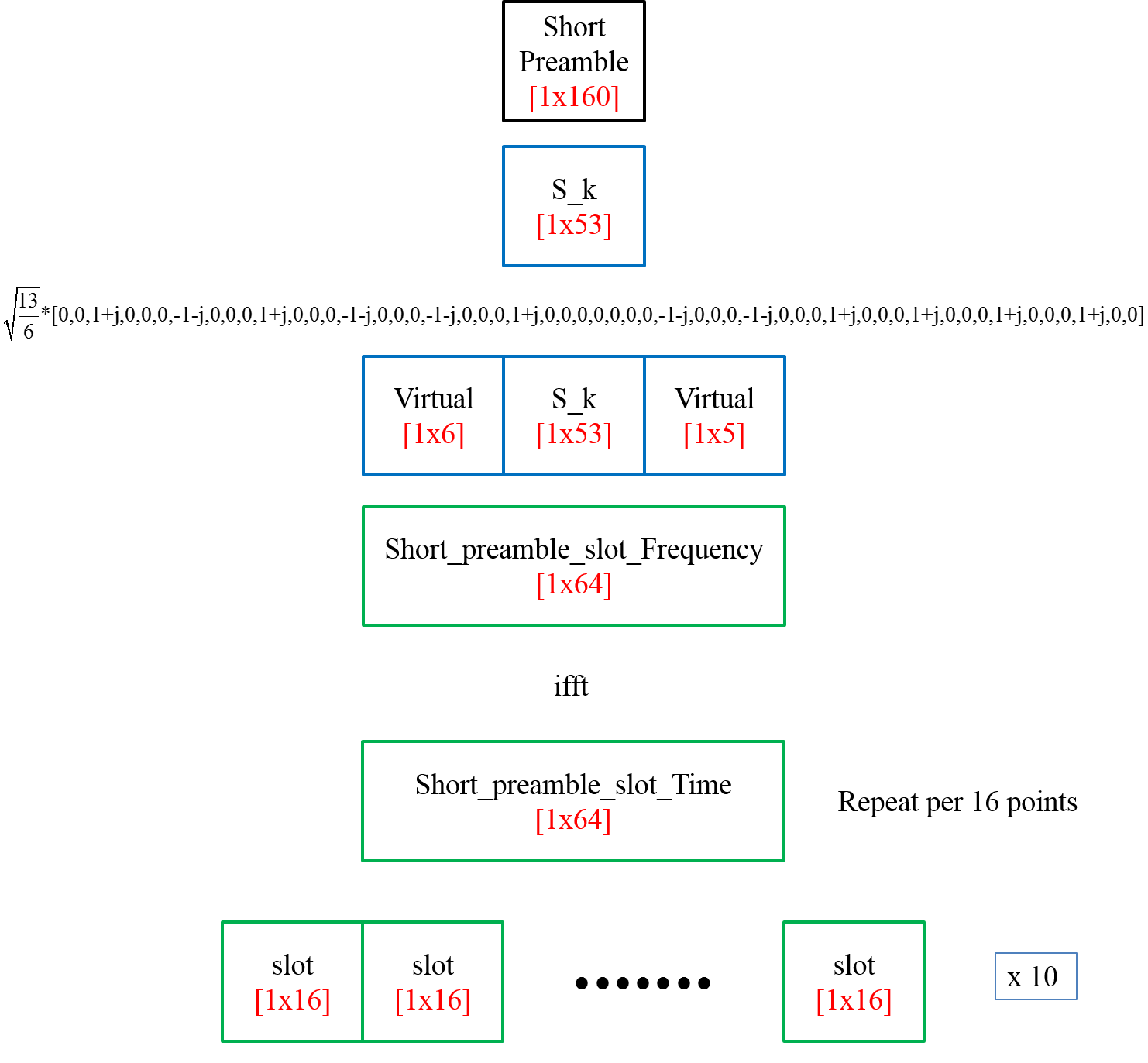

- Short Preamble

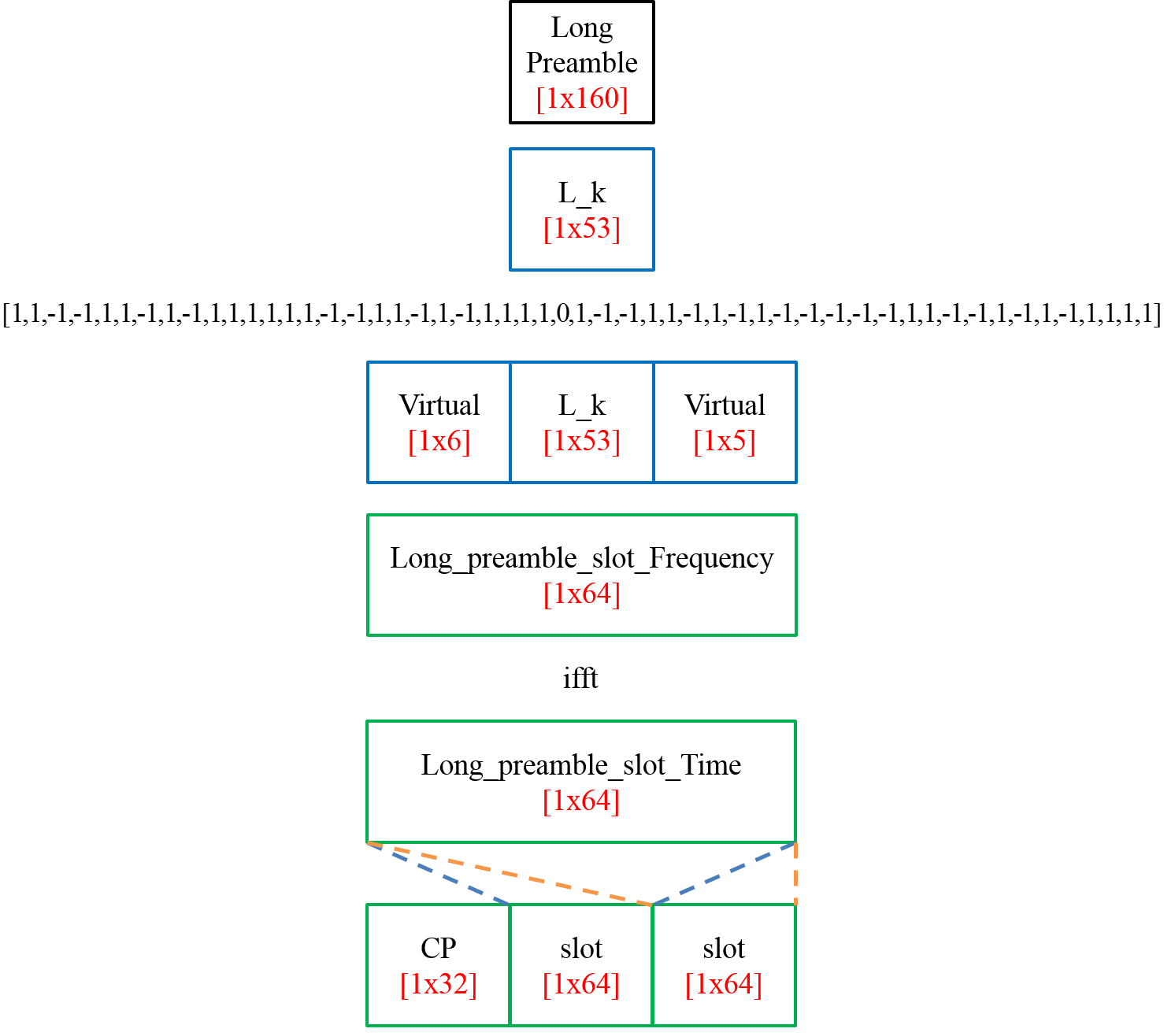

- Long Preamble

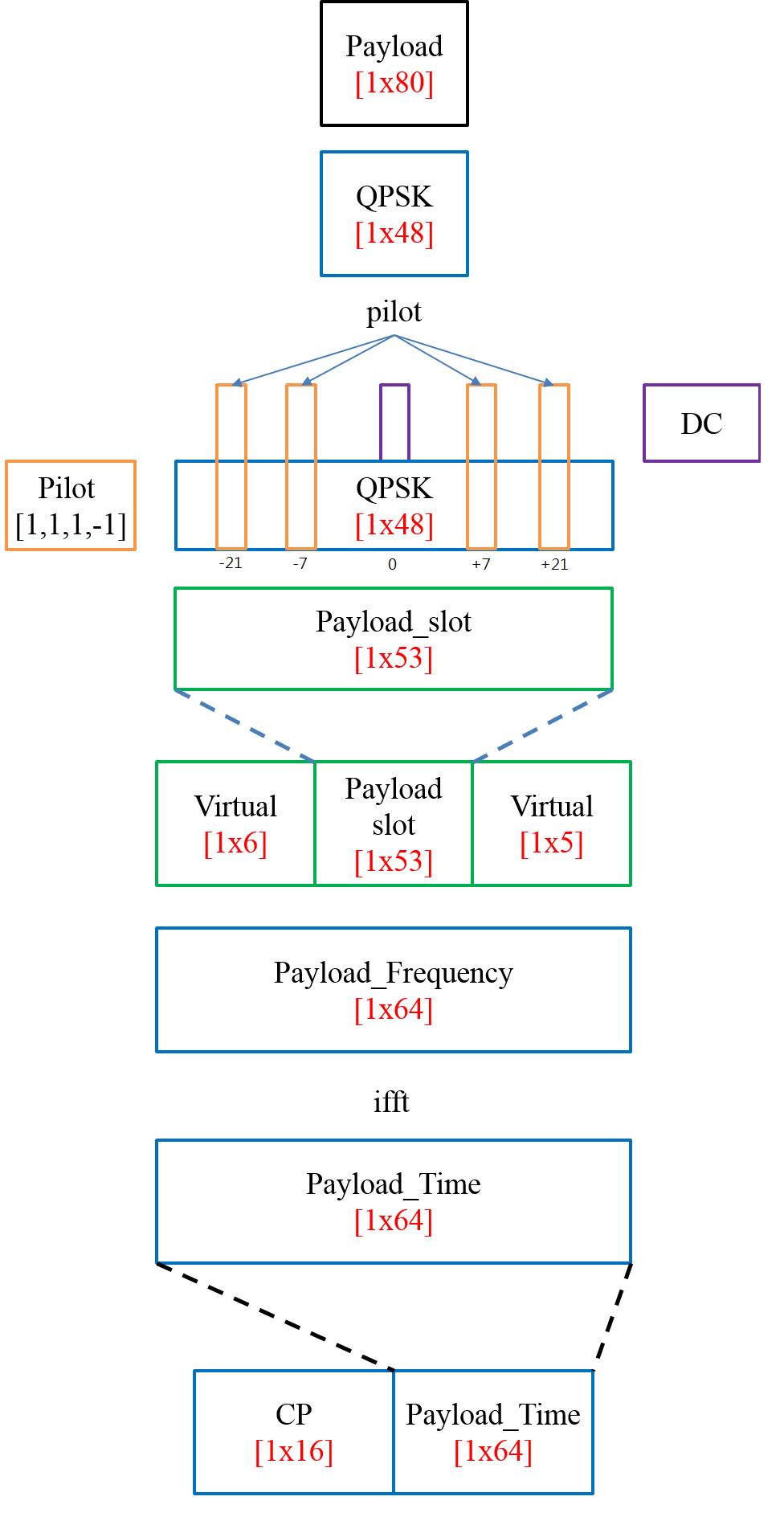

- Payload

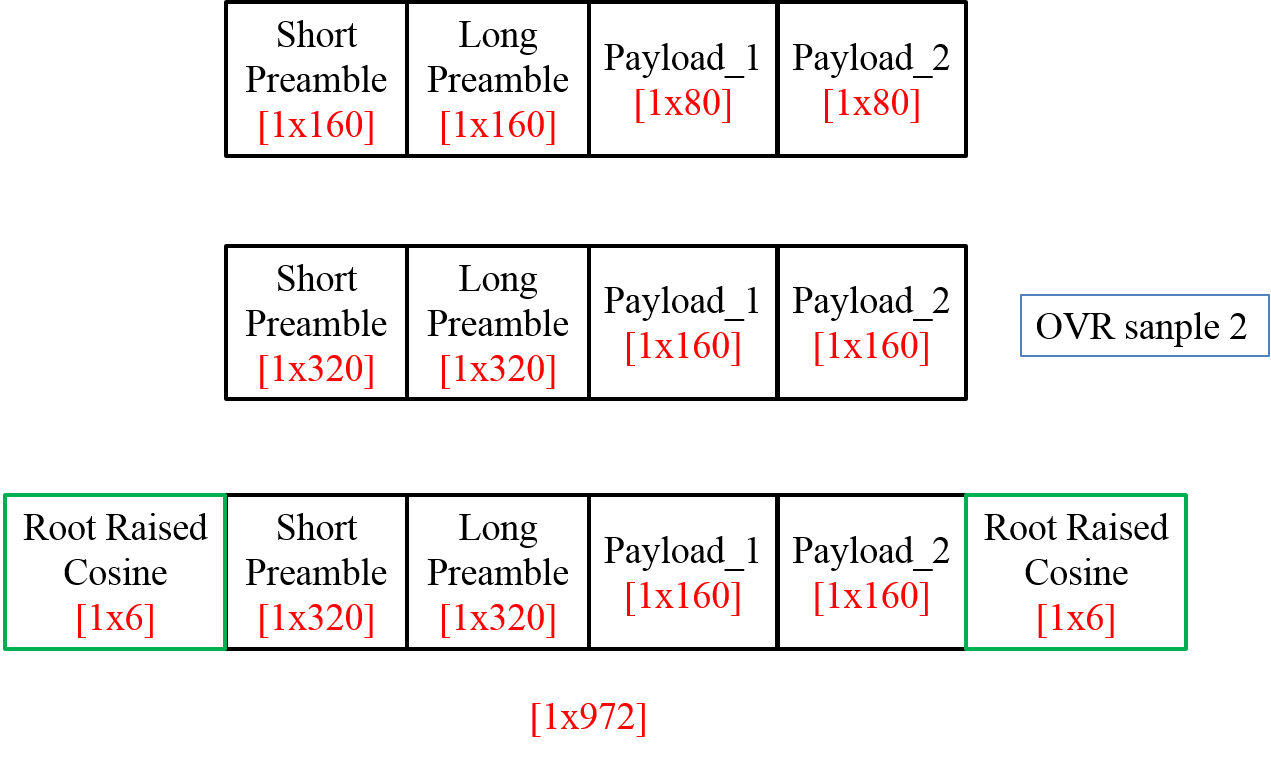

- TX signal

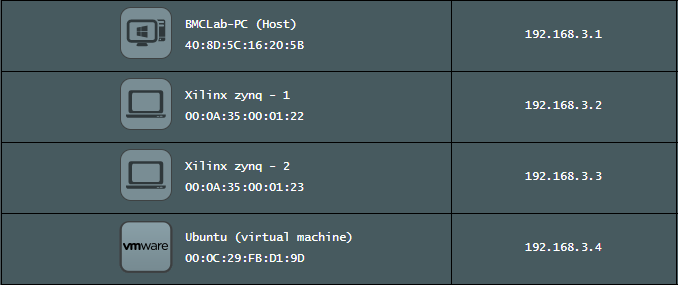

| Center Frequency | 5 GHz |

|---|---|

| Baseband Sample Rate (Bandwidth) | 20 MHz |

| Ts (Sampling time) | 50 ns |

| Samples Per Frame | 3000 |

| PC Host IP address | 192.168.3.1 |

| TX IP address | 192.168.3.2 |

| RX IP address | 192.168.3.3 |

Edit newip.sh file in SD card

# Flush existing config

ip addr flush dev eth0

ip link set dev eth0 down

# Set up new config

ip addr add 192.168.3.3/24 dev eth0

ip link set eth0 address 00:0A:35:00:01:23

ip route add default via 192.168.3.1

ip link set dev eth0 up

Then, use router DHCP hand setting mode to distribute network configuration parameters :

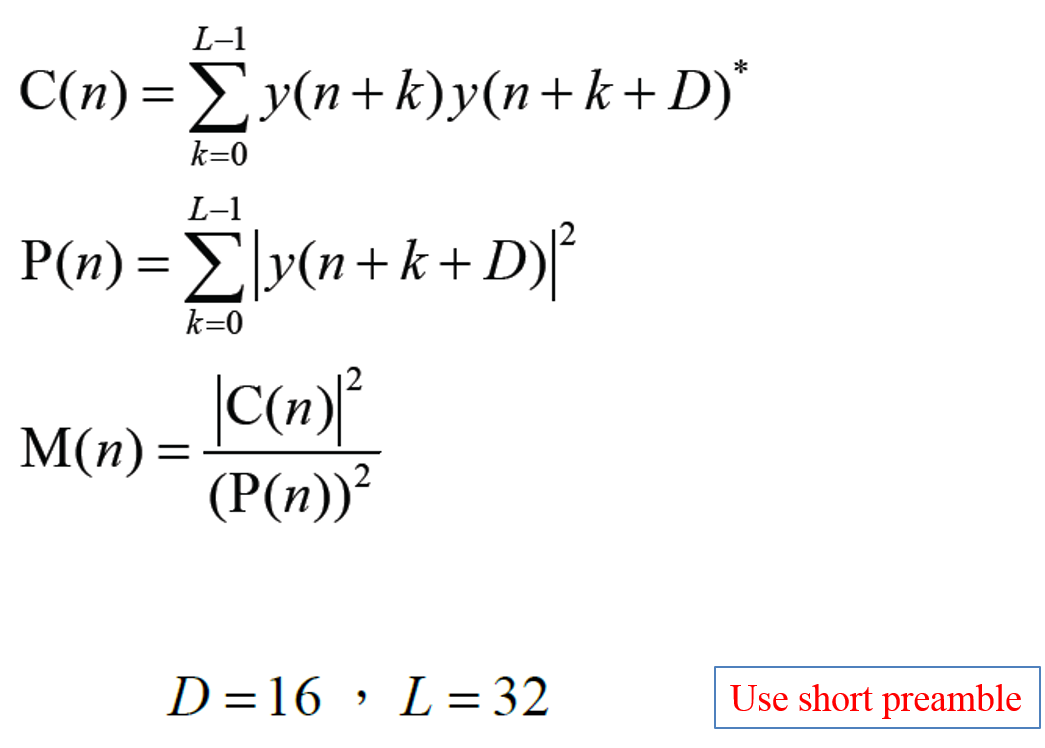

- "Delay and Correlate" algorithm for Packet Detection

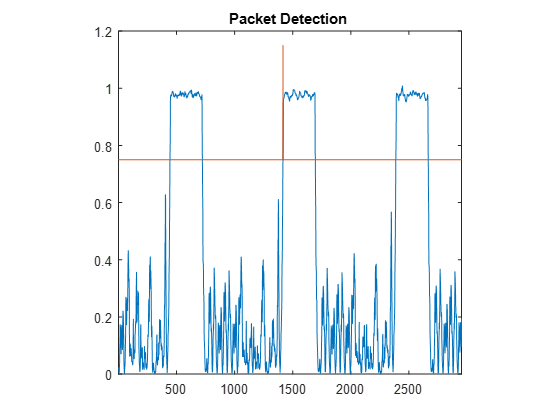

- Packet Detection (normal case) , Threshold=0.75

- Packet Detection (problem case & deselect the imperfect packet)

.png)

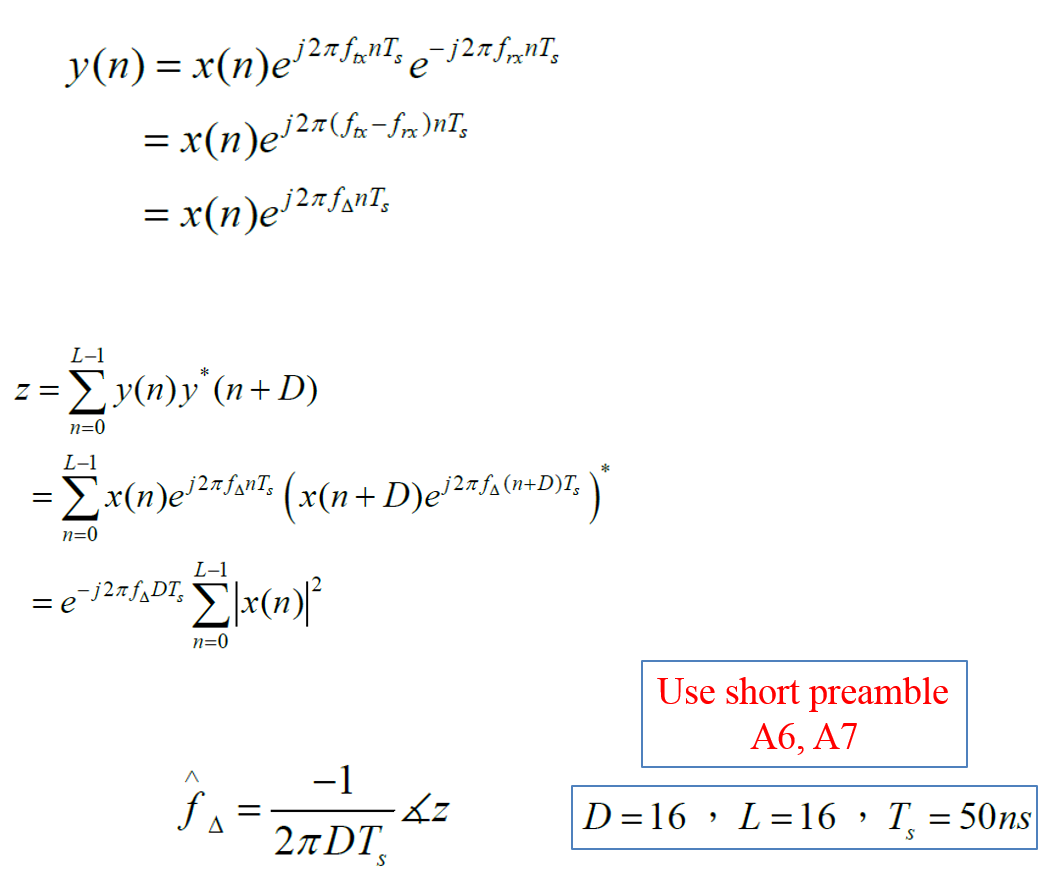

- Coarse CFO Estimation & Compensation

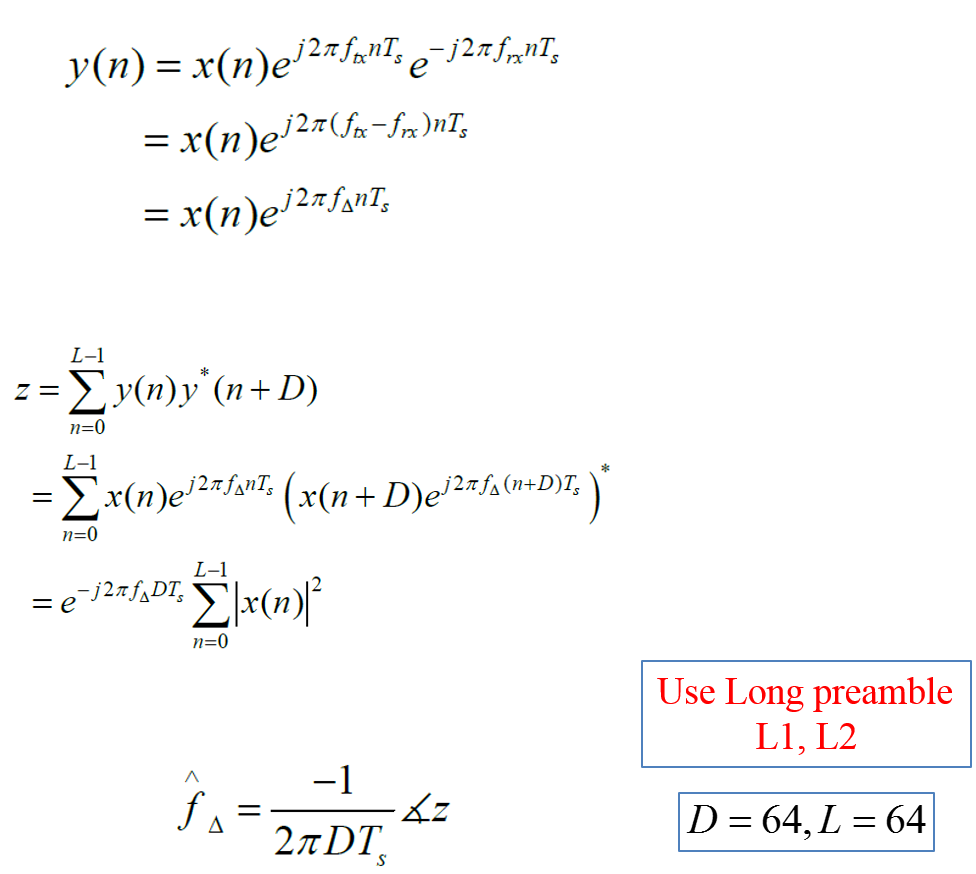

- Fine CFO Estimation & Compensation

- Channel Estimation & Equalizer