-

Notifications

You must be signed in to change notification settings - Fork 39

Home

|

|---|

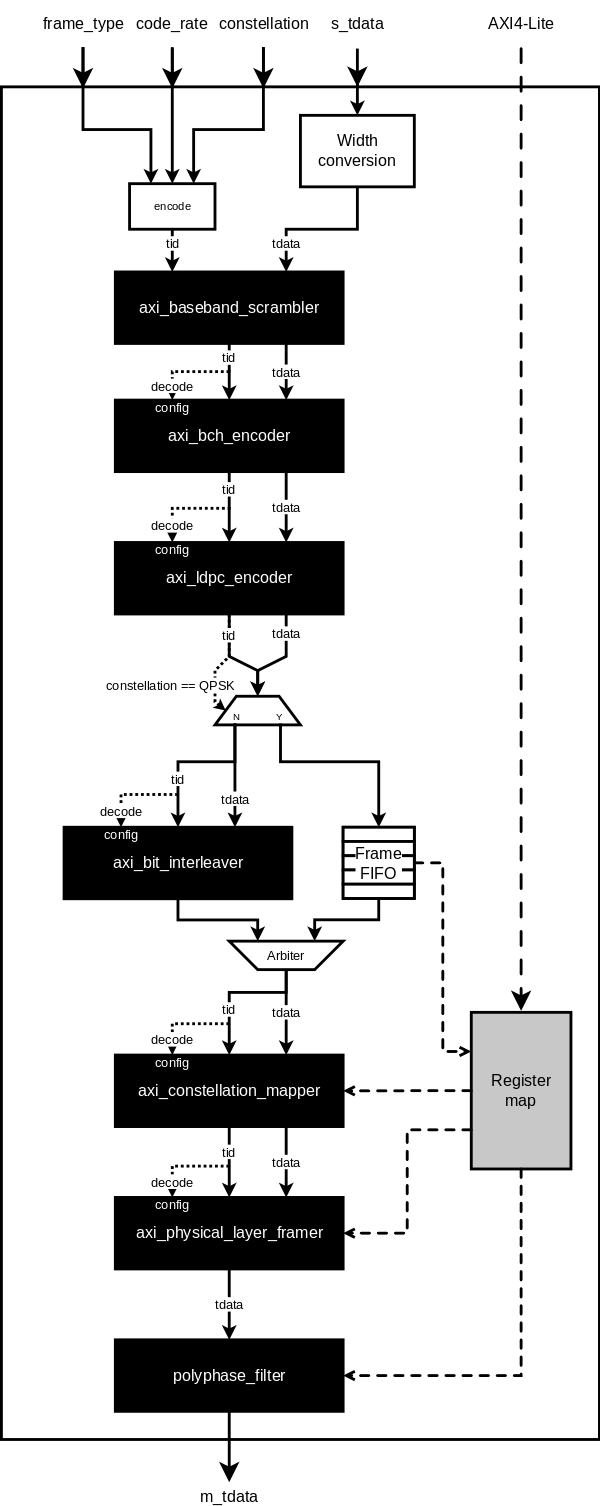

| DVB-S2 Tx block diagram |

This is the top module for the DVB-S2 transmitter, which instantiates the subcomponents needed by the standard. Note that a frame's configuration parameters accompanies the data using AXI's TID/TUSER, meaning each input frame can have different parameters.

|

|---|

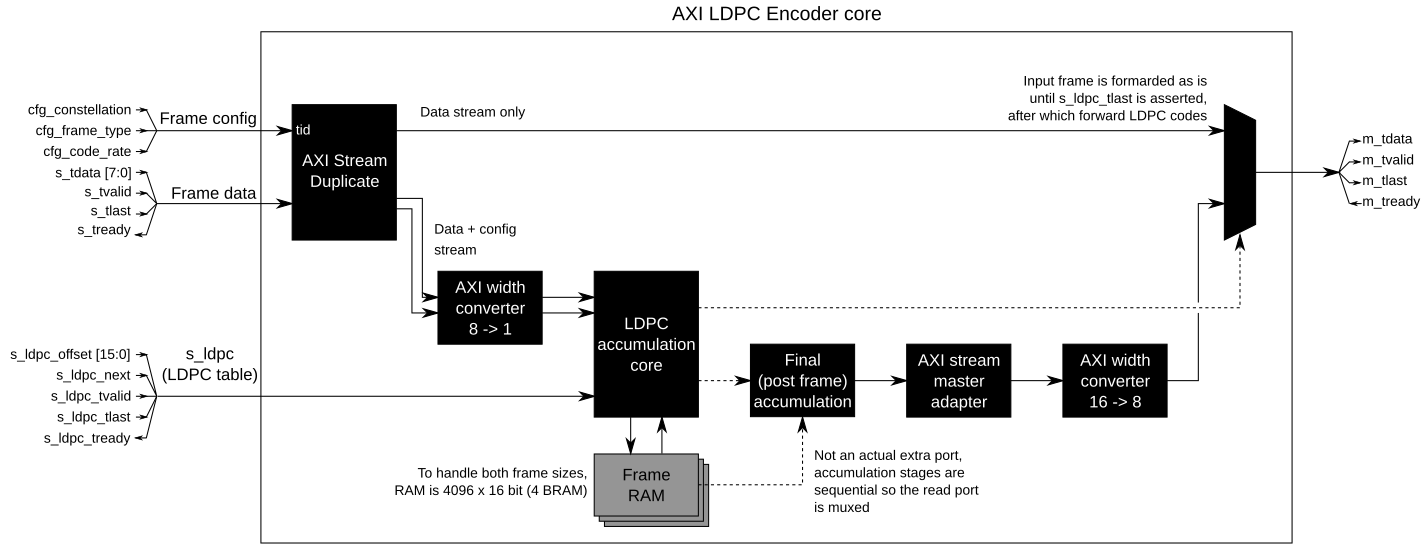

| AXI LDPC Encoder block diagram |

Data frame is fed to the frame data (s_tdata) and DVB parameters should be

synchronized with it.

Values from the DVB tables (Annexes B and C from ETSI EN 302 307-1 V1.4.1), are

expanded to per bit and fed to the s_ldpc interface. This interface need 2

values: the actual frame offsets (s_ldpc_offset) and when to process another

frame bit (s_ldpc_next).

When s_ldpc_tlast is received, accumulation is considered completed and the

final accumulation begins, in which point the component will not accept any data

until the output frame is fully written.

|

|---|

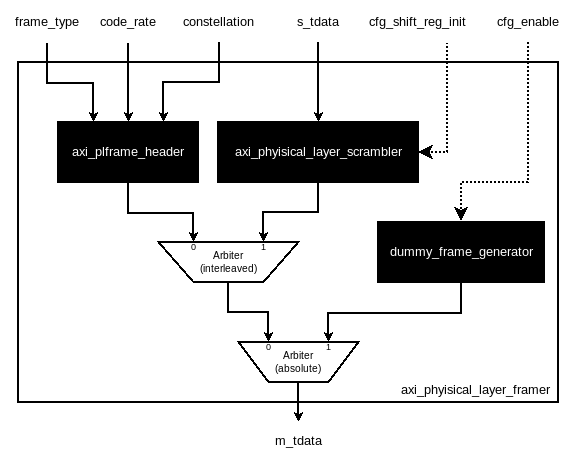

| AXI Physical Layer Framer block diagram |

Frame parameters are fed to the AXI PLFRAME Header block while data goes through the physical layer scrambler. The first arbiter is set up in interleaved mode to alternate between a header frame and a data frame. The resulting data stream is connected to a second arbiter whose other input is connected to the dummy frame generator. This arbiter is set up in absolute mode so that actual data frames take precedence over dummy frames.