-

Notifications

You must be signed in to change notification settings - Fork 14

Ethernet Switch

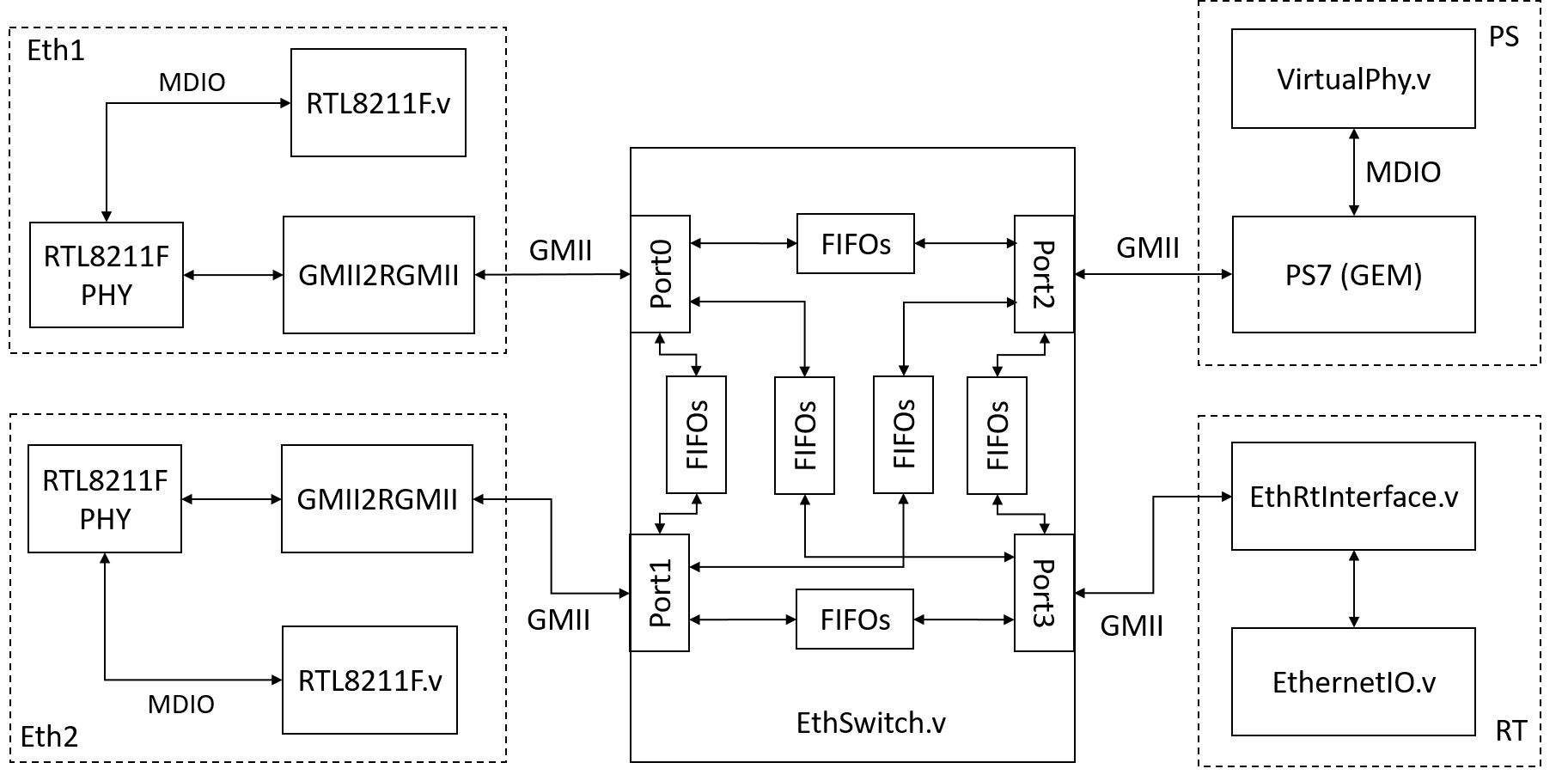

This page documents the Ethernet switch design for FPGA V3, which has two physical Ethernet ports (Eth1 and Eth2), each driven by an RTL8211F PHY, and two internal Ethernet devices, one in the Zynq ARM processor (PS) and a real-time device (RT) in the Zynq FPGA. Thus, in Firmware Rev 9, we implemented a 4-port Ethernet switch in the FPGA, with a GMII interface to each device (PHY or internal device), as shown in the following figure. Note that the 4 ports are numbered 0-3 and the implementation assumes that Ports 0-1 will be connected to the PHYs, Port 2 will be connected to the PS, and Port 3 will be connected to the RT.

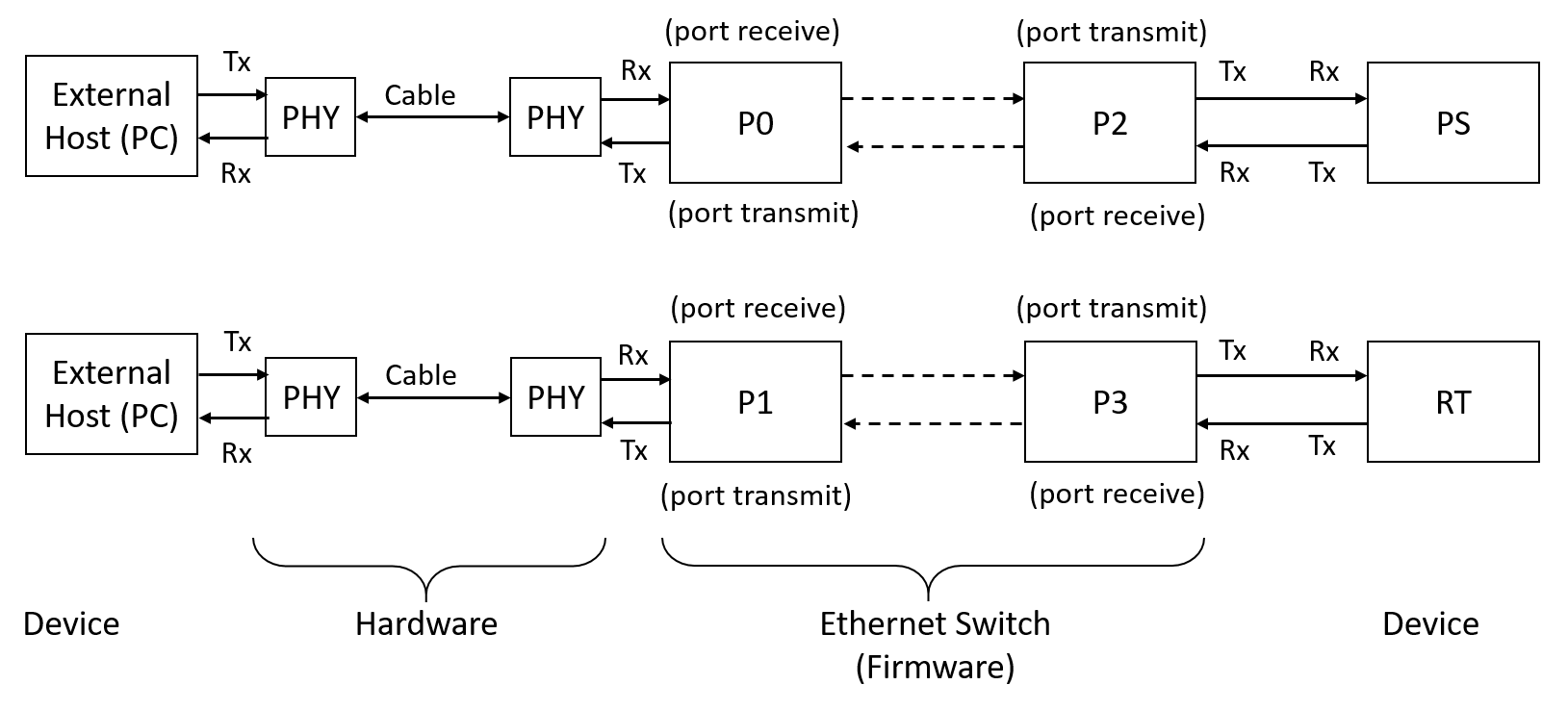

The following figure documents the high-level GMII connections between the external devices (via PHY) and the internal devices (PS and RT). Note that the Rx and Tx lines are swapped when connecting the internal devices to the Ethernet switch.

The Ethernet switch supports the standard GMII signals for each port (RxClk, RxValid, RxD, RxErr, TxClk, TxEn, TxD, TxErr). In addition, it supports the following signals for each port (In means input to switch):

| Signal | Direction | Description |

|---|---|---|

| Active | In | 1 -> Device is active (enabled) |

| Fast | In | 1 -> Device is fast (125 MHz clock) |

| DataReady | In | 1 -> Device has data to send to switch |

| RecvReady | In | 1 -> Device is ready to receive data |

| TxInfo | Out | 4 bits of packet info from switch (see below) |

| TxSrc | Out | Source port for data being transmitted (0-3) |

TxInfo is a 4-bit value:

- Bit 3 (MSB) is 1 if the source port is slow

- Bit 2 is 1 if there was a FIFO overflow

- Bit 1 is 1 if there was an IPv4 header checksum error

- Bit 0 (LSB) is 1 if there was a frame CRC error Currently, it is not used in the firmware.

In addition to the per-port signals, the Ethernet switch provides signals to help the RT implementation (EthernetIO) determine whether this board is the Hub (directly connected to PC via Ethernet) or the Broadcast Hub (closest to PC of all boards participating in broadcast read protocol).