-

Notifications

You must be signed in to change notification settings - Fork 5

Home

korben.dong edited this page Nov 26, 2020

·

11 revisions

- 简单,易于部署

- 插件化,易于扩展

- 静态化,设计与sulp无关,每一步的输出都可以被其他工具介入

- 易于构建flow

- 统一的flow规范

- 规范导入的设计文件

- 发挥gulp task的优势: 分割组合task/创建替换task.....

- 报告rpt做独立收集

- 以IP设计为中心的flow,收集IP相关的数据:git-config/vpp-config/mem/port/interface/testcase

- file - 归档

- run/build - 执行的flow任务

- report - 收集报告,生成信息

- regression - 生成run/build与report的pattern

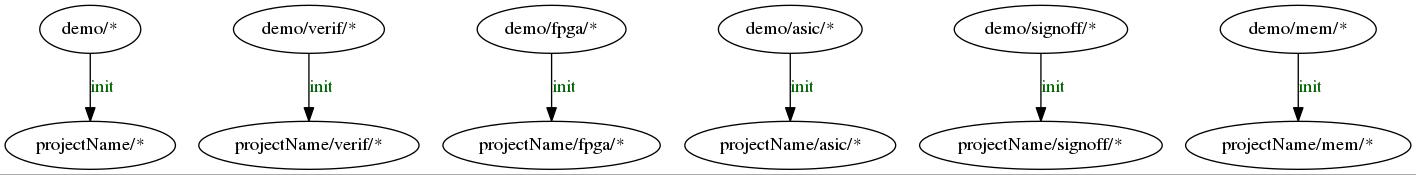

demo/

├── README.md

├── asic

├── config

│ ├── json

│ └── proj_config

├── docs

├── fpga

│ └── demo

├── rtl

├── signoff

├── sourceme.bash

├── sourceme.csh

├── toolchain

├── verif

│ └── demo

└── work.ts

- project 存放多个不同的work

例如,demo是一个项目,目录下保护多个work,verif是验证的workspace,asic是针对不同工艺做SoC级综合的workspace,fpga是FPGA流程的workspace,signoff是使用EDA工作做静态分析的workspace。

- work 存在project之下,包含自己的配置文件work.ts

以verif这个验证的workspace为例, demo是一个work,针对不同的testbench还可以建立其他类似verif/demo的work。

- init

- new:verif

- new:asic

- new:fpga

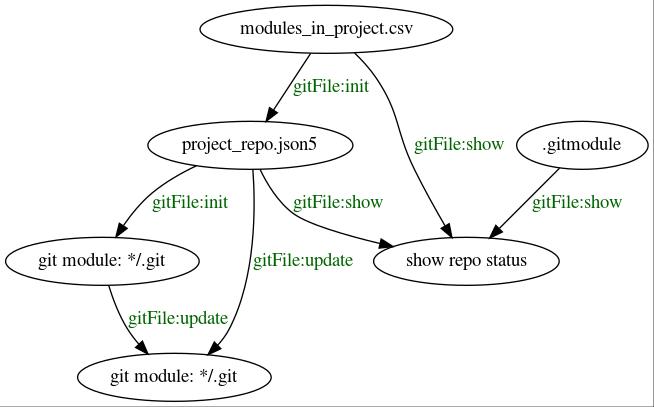

- git_file

- vpp_file

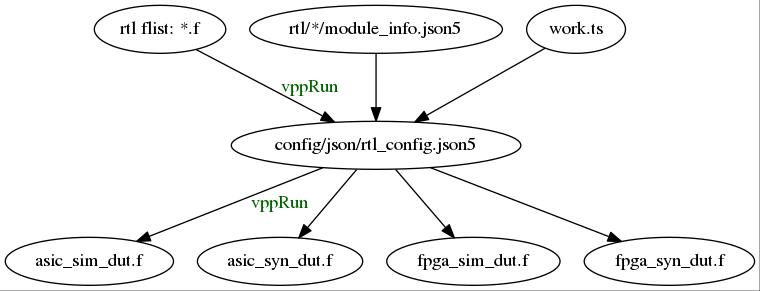

- vpp_run

- mem_file

- mem_verif

- mem_report

- mem_regression

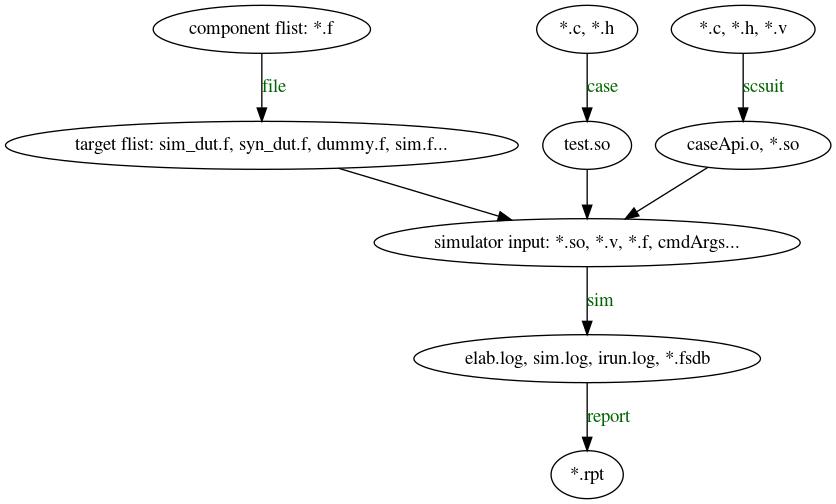

- verif_file

- verif_case

- verif_scSuit

- verif_uvm

- verif_sim

- verif_report

- verif_regression

- verif_wave

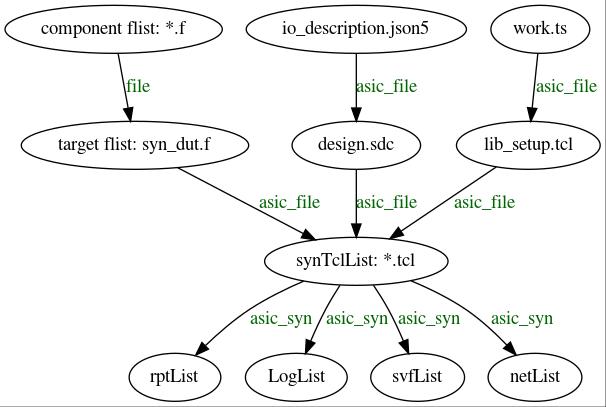

- asic_file

- asic_constrain

- asic_syn

- asic_report

- asic_regression

- asic_view --> start_gui

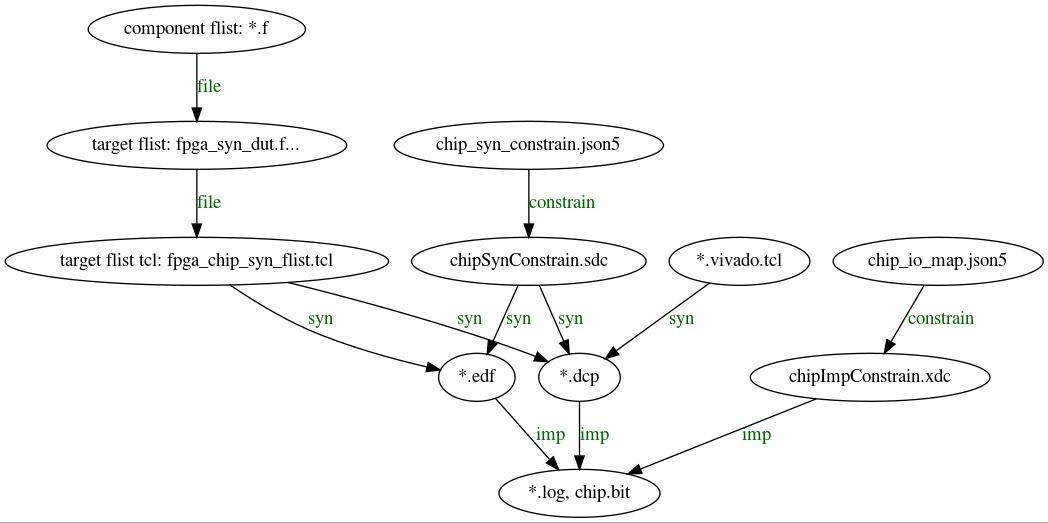

- fpga_file

- fpga_constrain

- fpga_syn

- fpga_imp

- fpga_report

- fpga_regression

- fpga_view --> start_gui

- signoff_file

- signoff_spyglass

- signoff_pt

- signoff_fm

- signoff_report

- signoff_regression

- ci_file

- ci_run

- ci_report

-

Quick Links

-

A Short Users Guilde to Chisel

-

Appendix

Release Notes